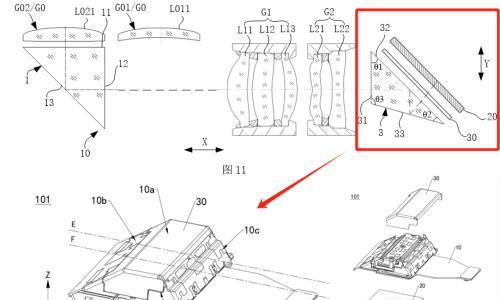

在2025年IEEE VLSI研讨会上,SK海力士首次披露了未来30年的DRAM技术发展蓝图,提出通过垂直栅极结构(4F² VG)和3D堆叠技术突破制程瓶颈。首席技术官Cha Seon Yong指出,随着传统平面架构逼近物理极限,公司计划在10nm以下节点采用4F² VG平台,该技术通过垂直布局单元面积缩减至传统结构的四分之一,结合混合键合工艺,可实现更高密度与能效。

针对3D DRAM成本争议,Cha Seon Yong强调技术创新将平衡层数增加带来的经济性挑战。此次路线图凸显了SK海力士在内存技术可持续演进中的前瞻布局,为行业应对摩尔定律放缓提供了新思路。

扫一扫关注微信

扫一扫关注微信